Petit-déjeuner de la science et de l’innovation

Jeudi 12 février 2015, 8h30, Hôtel de l’Industrie, Paris

Pendant des dizaines d’années, les concepteurs de microprocesseurs cherchaient leurs sources de progression dans la loi de Moore qu’il conviendrait plutôt d’appeler la « conjecture de Moore », suivie scrupuleusement de 1971 à 2001, période pendant laquelle le nombre de transistors intégrés sur un microprocesseur, donc sa puissance de calcul a doublé tous les deux ans et que le prix de ces composants chutait. La course aux « GHz » s’est développée parallèlement grâce à la réduction des dimensions des composants et des éléments parasites qui leur sont associés. Une butée a cependant été atteinte vers les années 2000 par Intel avec son « Intel Pentium 4 » entre 2 et 3 GHz à cause d’une génération thermique excessive difficile à gérer. Simultanément, le coût industriel de chaque nouveau saut technologique (du micron au nanomètre) continuait à augmenter et simultanément, le nombre des fabricants maîtrisant ces technologies diminuait.

Plutôt que de continuer à accroître la taille et la vitesse des processeurs, les concepteurs de microprocesseurs ont cherché progressivement à paralléliser les tâches à effectuer et à les confier à des processeurs multi-cœurs travaillant simultanément sur chacune d’entre elles.

C’est IBM qui a commercialisé le premier processeur multi-cœur dit professionnel «Power 4 » en 2001. Intel et AMD ont, quant à eux, commercialisé les premiers processeurs muti-cœur pour le marché de l’ordinateur personnel en 2005.

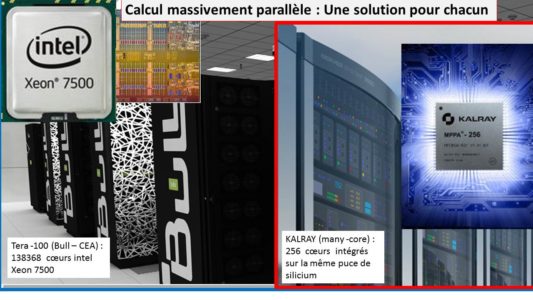

La puissance de calcul maintenant requise pour la mécanique des fluides, la météorologie, le décryptage des messages, le traitement de l’information et des données…, se mesure en pétaFLOPS (un pétaFLOP correspond à 10^15 opérations par seconde) et l’on va vers l’exaflop. De tels besoins sont couverts par l’industrie nationale. Ainsi le supercalculateur TERA-100, réalisé par Bull et acquis par le CEA se classe à la sixième place mondiale avec 1,25 pétaFLOPS de puissance crête théorique de calcul. Il est constitué de 17 480 processeurs octo-cœurs Intel Xeon soit près de 140 000 cœurs en tout. Mais dans le « très petit » aussi on rencontre maintenant des multi-processeurs, par exemple les appareils mobiles, mis à contribution pour implanter par exemple des moyens d’interface intelligents par la reconnaissance de la parole ou de l’image.

Ce déploiement de la loi de Moore a donc nourri et rythmé le développement des technologies de l’information dans toutes ses dimensions cumulées : grands ordinateurs pour le calcul ou le traitement de données, systèmes d’information d’entreprise, ordinateurs personnels, mobiles, systèmes embarqués, objets connectés, avec un Internet et un web de plus en plus puissant et capillaire.

Nous sommes au début, dans chacune de ces dimensions – et sans doute dans de nouvelles, par exemple le corps humain –, de bouleversements activement recherchés : la compréhension du cerveau et de l’intelligence et sa mise en œuvre in silico ; la compréhension approfondie et détaillée du monde du vivant, et sa fonctionnalisation dans une ingénierie révolutionnaire en médecine ou en biologie synthétique ; l’autonomisation des objets qui nous entourent, comme les voitures ; ou avec de nouvelles fonctions, comme les robots de service. Pour mettre la puissance de calcul nécessaire à ces développements, l’utilisation de milliers ou de millions de processeurs est inévitable.

Pour instrumenter ces révolutions, il faut les briques matérielles et logicielles de base. Kalray conçoit et commercialise une nouvelle génération de processeurs « manycore » fournissant aux applications puissance de calcul et basse consommation, par exemple dans le traitement de l’image et du signal, l’Internet, le calcul intensif et massif, le contrôle industriel ou robotique, la sécurité des données, les transports autonomes et sûrs. Sa série MPPA (Multi Purpose Processor Array) intègre à ce jour 256 processeurs de calcul sur une seule puce silicium d’un cm² travaillant plutôt vers 500 MHz et consommant globalement entre 10 et 100 fois moins pour le même traitement. Le processeur est mis entre les mains des développeurs à travers un ensemble d’outils de développements logiciels.

Les intervenants de notre matinale exposeront la vision et la problématique du calcul parallèle et des architectures qu’il impose. Ils parleront des principaux acteurs mondiaux et nationaux du domaine ainsi que de leurs projets et ambitions.

Avec Jean-Luc Dormoy, ancien élève de l’ENS Saint-Cloud, agrégé de mathématiques, docteur en intelligence artificielle, co-fondateur des sociétés Kalray et VESTA-System, Benoît Dupont de Dinechin, diplômé de l’ENSAE, docteur en Computer Sciences, directeur du développement Software et Chief Technology Officer de Kalray, et Patrick Demichel, diplômé de la Control Data Academy, Distinguished Technologist de Hewlett Packard, Senior Architect in Strategic Systems for EMEA à Hewlett Packard

Petits-déjeuners de la science et de l’innovation

Les Petits-déjeuners de la science et de l’innovation donnent la parole à l’industrie et à la recherche, qui font le point sur une innovation technologique susceptible d’avoir un impact fort sur nos économies et nos sociétés.

Un jeudi par mois, de 8h30h à 10h

(accueil à 8h autour d’un buffet petit-déjeuner et début de la rencontre à 8h30 précises)

à l’Hôtel de l’Industrie, 4 place Saint-Germain-des-Prés, 75006 Paris

Entrée gratuite, dans la limite des places disponibles. Inscription préalable obligatoire auprès du secrétariat de l’AFAS.

Partenariat AFAS – Société d’encouragement pour l’industrie nationale – Rayonnement du CNRS